# Compiling Polychronous Programs into Conditional Partial Orders for ASIP Synthesis

Sandeep K. Shukla, FERMAT Lab, Virginia Tech.

with Mahesh Nanjundappa, FERMAT Lab, Virginia Tech.

## Motivation

## Current trends in hardware requirements

- ↑Performance, ↓Latency, ↓Power Consumption, ↓Form Factor

- <sup>^</sup>Programmability for enabling reuse of components

- *Flexibility* to introduce late specification changes

## Motivation

## Current trends in hardware requirements

- ↑Performance, ↓Latency, ↓Power Consumption, ↓Form Factor

- <sup>^</sup>Programmability for enabling reuse of components

- **†**Flexibility to introduce late specification changes

## Application Specific Instruction-set Processors (ASIPs)

- Designed to exploit special characteristics of class of applications

- Reuse of components based on programmable modes of operation

- Custom instruction sets allow to maintain a level of flexibility

- Balance between ASICs and general purpose processors

## Requirements

Design methodologies for ASIPs should provide,

- Compact & efficient way to describe & store instruction sets

- Identify parallelism and express modes of operation

- A way to express available and required resources and map them

- Encoding of instruction sets for various optimization criteria

## Requirements

Design methodologies for ASIPs should provide,

- Compact & efficient way to describe & store instruction sets

- Identify parallelism and express modes of operation

- A way to express available and required resources and map them

- Encoding of instruction sets for various optimization criteria

## Conditional Partial Order Graphs (CPOGs) offer these facilities!

#### Motivation

Introduction to CPOGs Introduction to MRICDF MRICDF Models to CPOGs Analysis and ASIP Synthesis Conclusion and Future

# Outline of the talk

- 1 Motivation

- 2 Introduction to CPOGs

- Introduction to MRICDF

- MRICDF Models to CPOGs

- **5** Analysis and ASIP Synthesis

- 6 Conclusion and Future

Introduction Definitions Encoding instructions sets using CPOGs Composition of Instruction Sets

# Outline of the talk

## Motivation

- 2 Introduction to CPOGs

- Introduction to MRICDF

- 4 MRICDF Models to CPOGs

- 5 Analysis and ASIP Synthesis

- 6 Conclusion and Future

Introduction Definitions Encoding instructions sets using CPOGs Composition of Instruction Sets

### Conditional Partial Order Graphs

- A compact semantic model to express and compose large partial order sets

- Yields itself very easy for transformations, refinements, optimizations and encodings

- Graphically they can be visualised as hierarchical, annotated, weighted, directed graphs

Introduction Definitions Encoding instructions sets using CPOGs Composition of Instruction Sets

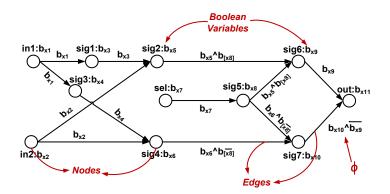

Formally CPOG is represented as a quintuple  $G = \langle V, E, X, \rho, \phi \rangle$

- V is a set of *nodes* which corresponds to events/atomic actions in a system that is being modelled.

- E ⊆ V × V is a set of directed *edges* between the *nodes*. An edge from node n to node m, indicates action m depends on n.

- X is a set of n Boolean variables. Each Boolean variable could be assigned values {0,1} resulting in unique 2<sup>n</sup> possible codes.

- $\rho$  is a *restriction function* defined on the set of Boolean variables in X as  $\rho \in \mathcal{F}(X)$ , where  $\mathcal{F}(X)$  is the set of all Boolean functions on the Boolean variables in X.

- Function  $\phi : (V \cup E) \to \mathcal{F}(X)$ . It assigns a Boolean condition  $\phi(z)$  to every node and edge z in the graph G.

Introduction Definitions Encoding instructions sets using CPOGs Composition of Instruction Sets

### Example of CPOG

Figure: Graphical representation of CPOG

Introduction Definitions Encoding instructions sets using CPOGs Composition of Instruction Sets

## Example : Simple adder/subtractor application

- Does add or subtract based on select signal

- Table below shows micro-steps of instructions for example

| Adder(A=A+B; <i>select</i> )       | Subtractor(A=A-B; <i>select</i> )  |  |

|------------------------------------|------------------------------------|--|

| <i>I</i> <sub>1</sub> :Load A      | <i>I</i> <sub>1</sub> :Load A      |  |

| <i>I</i> <sub>2</sub> :Load B      | <i>I</i> <sub>2</sub> :Load B      |  |

| <i>I</i> <sub>3</sub> :Compute A+B | <i>I</i> <sub>5</sub> :Compute A-B |  |

| <i>I</i> <sub>4</sub> :Store A     | <i>I</i> <sub>4</sub> :Store A     |  |

Introduction Definitions Encoding instructions sets using CPOGs Composition of Instruction Sets

## Example : Simple adder/subtractor application

- Does add or subtract based on select signal

- Table below shows micro-steps of instructions for example

| Adder(A=A+B; <i>select</i> )       | Subtractor(A=A-B; <i>select</i> )  |  |

|------------------------------------|------------------------------------|--|

| <i>I</i> <sub>1</sub> :Load A      | <i>I</i> <sub>1</sub> :Load A      |  |

| <i>I</i> <sub>2</sub> :Load B      | <i>I</i> <sub>2</sub> :Load B      |  |

| <i>I</i> <sub>3</sub> :Compute A+B | <i>I</i> <sub>5</sub> :Compute A-B |  |

| <i>I</i> <sub>4</sub> :Store A     | <i>I</i> <sub>4</sub> :Store A     |  |

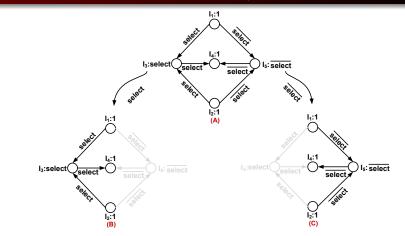

• Representing this instructions as CPOG H

• Create 5 nodes:

$$I_1, I_2, I_3, I_4, I_5$$

• Create 6 edges:

$$I_1 \xrightarrow{select} I_3$$

,  $I_2 \xrightarrow{select} I_3$ ,  $I_3$ ,  $I_3 \xrightarrow{select} I_4$ ,

$I_1 \xrightarrow{select} I_r$ ,  $I_2 \xrightarrow{select} I_r$ ,  $I_2 \xrightarrow{select} I_4$ ,

• Create Boolean variable set

$$X = \{select\}$$

• Establish  $\rho$  and  $\phi$  functions

Introduction Definitions Encoding instructions sets using CPOGs Composition of Instruction Sets

## Encoding

- Atomic actions  $I_1$  and  $I_2$  can be executed concurrently or sequentially

- Atomic action  $I_2$  has to be executed before  $I_3$

- Partial order on the set of micro-steps/atomic actions

- Assigning values from the set {0,1} to variables of X, to get unique Boolean vectors

- Unique vectors can be used as opcodes for instructions

Introduction Definitions Encoding instructions sets using CPOGs Composition of Instruction Sets

### CPOG representing execution of Simple adder/subtractor application

Figure: (A) Graphical representation of CPOG H, (B)  $H|_{select}$ , (C)  $H|_{select}$

Introduction Definitions Encoding instructions sets using CPOGs Composition of Instruction Sets

### Composition of Instruction sets

- Instruction is a pair  $\mathcal{I} = (\phi, H|_{select})$ , where  $\phi$  is the opcode and  $H|_{select}$  is the partial order

- Instruction set  $\mathcal{IS}$  is a set of instructions  $\mathcal{IS} = \{\mathcal{I}_1, \mathcal{I}_2, ..\}$ , such that each  $\mathcal{I}_k$  has a different opcode  $\phi$

Introduction Definitions Encoding instructions sets using CPOGs Composition of Instruction Sets

### Composition of Instruction sets

- Instruction is a pair  $\mathcal{I} = (\phi, H|_{select})$ , where  $\phi$  is the opcode and  $H|_{select}$  is the partial order

- Instruction set  $\mathcal{IS}$  is a set of instructions  $\mathcal{IS} = \{\mathcal{I}_1, \mathcal{I}_2, ..\}$ , such that each  $\mathcal{I}_k$  has a different opcode  $\phi$

- Composition of 2 instruction sets  $\mathcal{IS}_i$  and  $\mathcal{IS}_k$

- Is defined as  $\mathcal{IS}_i \cup \mathcal{IS}_k$

- Is defined only when no instruction in set *IS<sub>i</sub>* has same opcode as any instruction in *IS<sub>k</sub>*

- Is not defined if there exists 2 instructions with same opcodes

- Composition of more than 2 instruction sets is done by performing pairwise composition in arbitrary order

Introduction Definitions Encoding instructions sets using CPOGs Composition of Instruction Sets

## Composition of Instruction sets

- Instruction is a pair  $\mathcal{I} = (\phi, H|_{select})$ , where  $\phi$  is the opcode and  $H|_{select}$  is the partial order

- Instruction set  $\mathcal{IS}$  is a set of instructions  $\mathcal{IS} = \{\mathcal{I}_1, \mathcal{I}_2, ..\}$ , such that each  $\mathcal{I}_k$  has a different opcode  $\phi$

- Composition of 2 instruction sets  $\mathcal{IS}_i$  and  $\mathcal{IS}_k$

- Is defined as  $\mathcal{IS}_i \cup \mathcal{IS}_k$

- Is defined only when no instruction in set *IS<sub>i</sub>* has same opcode as any instruction in *IS<sub>k</sub>*

- Is not defined if there exists 2 instructions with same opcodes

- Composition of more than 2 instruction sets is done by performing pairwise composition in arbitrary order

- Complexity of composition: Linear with respect to the total number of instructions

Introduction Definitions MRICDF Actors Clock Calculus

# Outline of the talk

- Motivation

- 2 Introduction to CPOGs

- 3 Introduction to MRICDF

- MRICDF Models to CPOGs

- 5 Analysis and ASIP Synthesis

- 6 Conclusion and Future

Introduction Definitions MRICDF Actors Clock Calculus

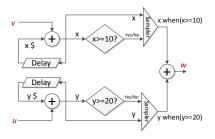

## MRICDF - Multi-Rate Instantaneous Communication Data Flow

- A Visual Language (with a textual substitute) to express a computation over concurrent streams of data

- MRICDF model is hierarchical composition of actors

- Actors are connected using channels

- Signal flows via channels

Figure: A simple MRICDF model

Introduction Definitions MRICDF Actors Clock Calculus

### Definitions

Definition (Event)

An occurrence of a fresh value on a signal constitutes an event

Introduction Definitions MRICDF Actors Clock Calculus

### Definitions

Definition (Event)

An occurrence of a fresh value on a signal constitutes an event

#### Definition (Signal)

A signal is a totally ordered sequence of events

Introduction Definitions MRICDF Actors Clock Calculus

### Definitions

Definition (Event)

An occurrence of a fresh value on a signal constitutes an event

#### Definition (Signal)

A signal is a totally ordered sequence of events

Definition (Instant set of a signal)

$\sigma(x)$  – set of all instants where signal x has events

Introduction Definitions MRICDF Actors Clock Calculus

### Definitions

#### Definition (Event)

An occurrence of a fresh value on a signal constitutes an event

#### Definition (Signal)

A signal is a totally ordered sequence of events

#### Definition (Instant set of a signal)

$\sigma(x)$  – set of all instants where signal x has events

#### Definition (Clock of a signal)

Instant set  $\sigma(x)$  is also known as clock of signal denoted by  $\hat{x}$

Introduction Definitions MRICDF Actors Clock Calculus

### Definitions

#### Definition (Event)

An occurrence of a fresh value on a signal constitutes an event

#### Definition (Signal)

A signal is a totally ordered sequence of events

#### Definition (Instant set of a signal)

$\sigma(x)$  – set of all instants where signal x has events

#### Definition (Clock of a signal)

Instant set  $\sigma(x)$  is also known as clock of signal denoted by  $\hat{x}$

Introduction Definitions MRICDF Actors Clock Calculus

### Definitions

#### Definition (Event)

An occurrence of a fresh value on a signal constitutes an event

#### Definition (Signal)

A signal is a totally ordered sequence of events

Definition (Instant set of a signal)

$\sigma(x)$  – set of all instants where signal x has events

#### Definition (Clock of a signal)

Instant set  $\sigma(x)$  is also known as clock of signal denoted by  $\hat{x}$

Definition (Synchronous Signals)

Signals x and y are called synchronous signals iff  $\hat{x} = \hat{y}$

Introduction Definitions MRICDF Actors Clock Calculus

## Definitions

## Definition (Data Dependence Relation)

• Multiple signals being read/written in an instant have a partial order - Dependency order

A dependency relation  $x \xrightarrow{[c]} y$ , indicates that the signal y is dependent on x, when condition c is true

• Data dependencies are not static, they change based on predicates

Introduction Definitions MRICDF Actors Clock Calculus

## **MRICDF** Actors

- MRICDF consists of 4 primitive actors

- Numerous derived actors, Ex: Logical And, Multiplication, etc

- Every actor has a predefined set of Rate Constraints

- User can specify various synchronization requirements by adding additional clock constraints

| Actor                   | Clock                                         | Data Dependency                     |

|-------------------------|-----------------------------------------------|-------------------------------------|

| definition              | Relations                                     | Relations                           |

| Function                | $\sigma(a) = \sigma(b) = \sigma(r)$           | a  ightarrow r                      |

| $r = a \star b$         | $\hat{a}=\hat{b}=\hat{r}$                     | b  ightarrow r                      |

| Buffer                  | $\sigma(y) = \sigma(x)$                       | No                                  |

| $y = x$ n init $v_1v_n$ | $\hat{y} = \hat{x}$                           | dependency                          |

| Sampler                 | $\sigma(y) = \sigma(x) \cap \sigma(z = true)$ |                                     |

| y = x when $z$          | $\hat{y} = \hat{x} \wedge [\hat{z}]$          | $x \xrightarrow{[z]} y$             |

| Merge                   | $\sigma(r) = \sigma(a) \cup \sigma(b)$        | a  ightarrow r                      |

| r = a default $b$       | $\hat{r}=\hat{a}ee{b}$                        | $b \xrightarrow{\hat{b}-\hat{a}} r$ |

Introduction Definitions MRICDF Actors Clock Calculus

## Clock Calculus

- Determining relations between clocks and analysing is done in a step called *Clock Calculus*

- Aim of clock calculus: To determine which signals participate in which reaction

- The signal that participates in each and every reaction -Master Trigger - multiple master triggers possible

- Clock of Master Trigger signal is Master Clock

- Clocks of signals that aren't master triggers can be derived based on predicates of either master clock or clocks of other known signals

- Hierarchically ordering these clocks gives us *Hierarchial Clock Relation Graph* (HCRG)

- Rooted HCRG : Clock Tree

# Outline of the talk

- 1 Motivation

- 2 Introduction to CPOGs

- Introduction to MRICDF

- MRICDF Models to CPOGs

- 5 Analysis and ASIP Synthesis

- 6 Conclusion and Future

POGs Merge Actor thesis Observations uture Composite Actor

**Buffer Actor**

Function Actor Buffer Actor Sampler Actor Merge Actor Observations Composite Actor

## CPOG for Function Actor

Operation:  $y = f(x_1, x_2, ..., x_n)$ , Clock relation:  $\hat{y} = \hat{x}_1 = \hat{x}_2 = ... = \hat{x}_n$ •  $V = \{y, x_1, x_2, ..., x_n\}$ •  $E = \{x_i \to y \mid x_i \in (x_1, x_2, ..., x_n)\}$ •  $X = \{\{b_{x_i}\} \cup \{b_{x_i} | x_i \in (x_1, x_2, ..., x_n)\}\},\$  $b_{y} = b_{x1} = b_{x2} = \dots = b_{xn}$ • Function  $\phi$  $x_n:b_{xn}$  $\phi(\mathbf{y}) = b_{\mathbf{y}},$  $\phi(x_1) = b_{x_1}.$  $x_3:b_{x_3}$  $\phi(x_n) = b_{x_n}$  $\phi(x_1 \rightarrow y) = b_{x_1}$  $\phi(x_2 \to y) = b_{x2},$ x5:bx5  $\phi(x_n \to v) = b_{x_n}$ Figure: CPOG for Function Actor

Sandeep K. Shukla, FERMAT Lab, Virginia Tech.

Polychronous Specifications to ASIP

15/30

Function Actor Buffer Actor Sampler Actor Merge Actor Observations Composite Actor

## CPOG for Buffer Actor

Operation: y = x \$ 1 *init c* Clock relation:  $\hat{y} = \hat{x}$

- $V = \{y, x\}$

- *E* = {}

- $X = \{b_y, b_x\}$

- $\rho = \{b_y = b_x\}$

- Function  $\phi$   $\phi(y) = b_y$  $\phi(x) = b_x$

## Figure: CPOG for Buffer Actor

Function Actor Buffer Actor Sampler Actor Merge Actor Observations Composite Actor

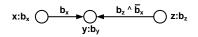

## CPOG for Sampler Actor

Operation: y = x when c Clock relation:  $\hat{y} = \hat{x} * [c]$ •  $V = \{v, x, c\}$ •  $E = \{x \rightarrow y, c \rightarrow y\}$ •  $X = \{b_v, b_x, b_c, b_{[c]}, b_{[\bar{c}]}\}$ ۵  $\rho = \left\{ \begin{array}{l} \left\{ b_y = b_x \wedge b_{[c]} \right\} \cup \\ \left\{ b_c = b_{[c]} \lor b_{[\bar{c}]} \right\} \cup \\ \left\{ b_{[c]} \land b_{[\bar{c}]} = false \right\} \end{array} \right\}$ • Function  $\phi$  $\mathbf{x}:\mathbf{b}_{\mathbf{x}} \bigcirc \overset{\mathbf{D}_{\mathbf{x}} \land \mathbf{D}_{[\mathbf{c}]}}{\longrightarrow} \bigcirc \overset{\mathbf{D}_{\mathbf{x}} \land \mathbf{D}_{[\mathbf{c}]}}{\longleftarrow}$  $\phi(\mathbf{y}) = b_{\mathbf{y}}$ c:b  $\phi(x) = b_x$  $\phi(c) = b_c$ Figure: CPOG for Sampler Actor

Function Actor Buffer Actor Sampler Actor Merge Actor Observations Composite Actor

## CPOG for Merge Actor

Operation: y = x default z Clock relation:  $\hat{v} = \hat{x} + \hat{z}$ •  $V = \{y, x, z\}$ •  $E = \{x \rightarrow y, z \rightarrow y\}$ •  $X = \{b_v, b_x, b_z\}$ •  $\rho = \{b_v = b_x \vee b_z\}$ • Function  $\phi$  $\phi(\mathbf{y}) = b_{\mathbf{y}}$  $\phi(x) = b_x$  $\phi(z) = b_{z}$  $\phi(x \to y) = b_x$  $\phi(z \rightarrow v) = b_z \wedge b_y$

Figure: CPOG for Merge Actor

Function Actor Buffer Actor Sampler Actor Merge Actor Observations Composite Actor

## Observations

## Observation

For each primitive actor A, if  $g_A$  represents the CPOG derived using the steps described above, then  $g_A$  contains all the necessary information for control of scheduling the execution of A.

### Observation

For primitive actors  $A_1$  and  $A_2$ , if  $g_{A_1}$  and  $g_{A_2}$  represents the corresponding CPOGs then for composition  $A_1 \mid A_2$ , the corresponding CPOG is the  $g_{A_1} \cup g_{A_2}$ .

Function Actor Buffer Actor Sampler Actor Merge Actor Observations Composite Actor

## Deriving CPOG for Composite Actor

- Combination of primitive actors that are used to express modular and hierarchical behavior

- First we derive the CPOGs of composite actors and then compose (∪) it with the CPOG of the rest of the model

- Algorithm 1 lists the method used to derive a CPOG for a composite actor

Function Actor Buffer Actor Sampler Actor Merge Actor Observations Composite Actor

## Algorithm 1: Algorithm to derive CPOG for a Composite Actor

```

Input: Composite Actor CA, Model M

Output: CPOG G = \langle V, E, X, \rho, \phi \rangle for CA

Initialize G = \langle \{\}, \{\}, \{\}, \{\}, \{\}, \{\} \rangle;

Let A_{NC} & A_{C} be partition of actors in CA into sets of Primitive(Non-composite) and Composite actors resp.

(present immediately under CA);

Let I_{CA} = \{p_1, p_2, \dots, p_n\} be the inports of CA;

Let O_{CA} = \{p_1, p_2, \dots, p_m\} be the outports of CA:

foreach composite actor a \in A_C do

//recursive call, ∪ represents composition of CPOGs

G \leftarrow G \cup composite\_cpog(a, M);

end

foreach primitive actor a \in A_{NC} do

//∪ represents composition of CPOGs

G \leftarrow G \cup primitive\_cpog(a):

end

foreach p_i \in I_{CA} \cup O_{CA} do

Let chin be the in-coming channel connected to pi;

Let pein be source port of the channel chin;

foreach out-going channel chout from p; do

Let peout be destination port of channel chout;

Let e_{new} = createEdge(p_{e_{in}}, p_{e_{out}});

E \leftarrow E \cup \{e_{new}\};

\phi(e_{new}) = \text{Constraints on } ch_{in} \&\& \text{Constraints on } ch_{out};

end

end

return G:

```

Function Actor Buffer Actor Sampler Actor Merge Actor Observations Composite Actor

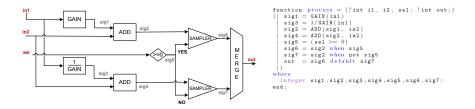

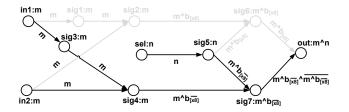

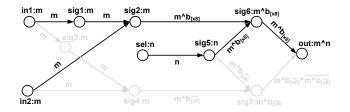

### Example MRICDF model

- Sample MRICDF model & its SIGNAL code

- ADD, Comparator, GAIN &  $\frac{1}{GAIN}$  are predefined function actors

Function Actor Buffer Actor Sampler Actor Merge Actor Observations Composite Actor

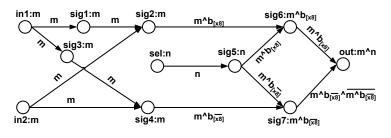

### CPOG for the Example MRICDF model

Figure: CPOG for the MRICDF Model

Function Actor Buffer Actor Sampler Actor Merge Actor Observations Composite Actor

#### Formal representation CPOG for the Example MRICDF model

| Quintuple | Set                                                                                                                                                              |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Element   | Elements                                                                                                                                                         |

| V         | $\{in1, in2, sel, out, sig1, sig2, sig3, sig4, sig5, sig6, sig7\}$                                                                                               |

| E         | $\{ \textit{in1}  ightarrow \textit{sig1}, \textit{in1}  ightarrow \textit{sig3}, \textit{in2}  ightarrow \textit{sig2}, \textit{in2}  ightarrow \textit{sig4},$ |

|           | $sig3  ightarrow sig4, \; sig1  ightarrow sig2, \; sig2  ightarrow sig6, \; sig4  ightarrow sig7,$                                                               |

|           | $sel 	o sig5,  sig5 	o sig6,  sig5 	o sig7,  sig6 	o out,  sig7 	o out \}$                                                                                       |

| Х         | $\{b_{x1}, b_{x2}, b_{x3}, b_{x4}, b_{x5}, b_{x6}, b_{x7}, b_{x8}, b_{[x8]}, b_{\overline{[x8]}}, b_{x9}, b_{x10}, b_{x11}\}$                                    |

| $\rho$    | $\{b_{x1} = b_{x2} = b_{x3} = b_{x4} = b_{x5} = b_{x6} = \mathbf{m}, \ b_{x7} = b_{x8} = \mathbf{n},$                                                            |

|           | $b_{x8} = b_{[x8]} \lor b_{\overline{[x8]}}, \ \textit{false} = b_{[x8]} \land b_{\overline{[x8]}}, \ b_{x9} = b_{x5} \land b_{[x8]},$                           |

|           | $b_{x10} = b_{x6} \wedge b_{\overline{[x8]}}, \ b_{x11} = b_{x9} \vee b_{x10}$                                                                                   |

| $\phi$    | $\{\phi(in1) = b_{x1}, \ \phi(in2) = b_{x2}, \ \phi(sig1) = b_{x3}, \ \phi(sig2) = b_{x5},$                                                                      |

|           | $\phi(sig3) = b_{x4}, \ \phi(sig4) = b_{x6}, \ \phi(sel) = b_{x7}, \ \phi(sig5) = b_{x8},$                                                                       |

|           | $\phi(sig6) = b_{x9}, \ \phi(sig7) = b_{x10}, \ \phi(out) = b_{x11}, \ \phi(in1 \rightarrow sig1) = b_{x1},$                                                     |

|           | $\phi(in1 \rightarrow sig3) = b_{x1}, \ \phi(in2 \rightarrow sig2) = b_{x2}, \ \phi(in2 \rightarrow sig4) = b_{x2},$                                             |

|           | $\phi({\it sig1}  ightarrow {\it sig2}) = b_{	imes 3}, \; \phi({\it sig3}  ightarrow {\it sig4}) = b_{	imes 4},$                                                 |

|           | $\phi(sig2 	o sig6) = b_{x5} \wedge b_{[x8]}, \ \phi(sig4 	o sig7) = b_{x6} \wedge b_{[\overline{x8}]},$                                                         |

|           | $\phi(sel \to sig5) = b_{x7}, \ \phi(sig5 \to sig6) = b_{x5} \land b_{[x8]},$                                                                                    |

|           | $\phi(sig5 \rightarrow sig7) = b_{x6} \wedge b_{\overline{[x8]}},$                                                                                               |

|           | $\phi(sig6  ightarrow out) = b_{x9}, \ \phi(sig7  ightarrow out) = b_{x10} \wedge \overline{b_{x9}} \}$                                                          |

Sandeep K. Shukla, FERMAT Lab, Virginia Tech.

Outline of the talk

Motivation

- 2 Introduction to CPOGs

- Introduction to MRICDF

- 4 MRICDF Models to CPOGs

- **5** Analysis and ASIP Synthesis

- 6 Conclusion and Future

Transformations Resource Estimation Implementability

Transformations Resource Estimation Implementability

- Initial CPOG needs to be simplified before transformations are applied

- Aim is to reduce the number of variables in set X

- $\bullet$  Use the equivalence relations in set  $\rho$

- Algorithm 2 lists the simplification step

# **Algorithm 2:** simplify(G): Simplify CPOG

Input: Un-simplified CPOG  $G = (V, E, X, \rho, \phi)$ Output: Simplified CPOG  $G = (V, E, X, \rho, \phi)$ Let  $\mathcal{E} = \{\text{Set of all Boolean equalities among single literals in } \rho\}$ ; Let  $(b_{x1}, b_{x2}, ..., b_{xn})$  represent the vector X; foreach  $b_{xi} \in V$  do if  $(b_{xi} = b_{xj}) \in \mathcal{E}$  then replace all occurrences of  $b_{xj}$  in  $\rho$  and  $\phi$  and simplify with idempotence and other Boolean simplification laws to obtain new  $\rho$ , and new  $\phi$ .  $X = X - \{b_{xj}\}$ ; end

Transformations Resource Estimation Implementability

# Proposition

Algorithm 2 converges and reduces the number of control states of the resulting system

**Proof:** Convergence is based on number of equivalence classes of control variables in X, and its reduction in each step

- Number of control states can be reduced further by proving more Boolean equivalences using powerful solvers like SMT solver

- Another way to reduce control states is by eliminating equivalent behaviors

Transformations Resource Estimation Implementability

# Proposition

Algorithm 2 converges and reduces the number of control states of the resulting system

**Proof:** Convergence is based on number of equivalence classes of control variables in X, and its reduction in each step

- Number of control states can be reduced further by proving more Boolean equivalences using powerful solvers like SMT solver

- Another way to reduce control states is by eliminating equivalent behaviors

- X is simplified

Transformations Resource Estimation Implementability

# Proposition

Algorithm 2 converges and reduces the number of control states of the resulting system

**Proof:** Convergence is based on number of equivalence classes of control variables in X, and its reduction in each step

- Number of control states can be reduced further by proving more Boolean equivalences using powerful solvers like SMT solver

- Another way to reduce control states is by eliminating equivalent behaviors

- X is simplified

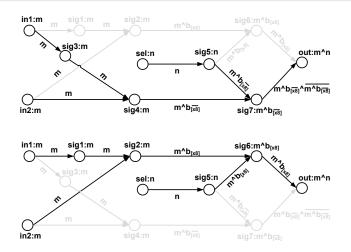

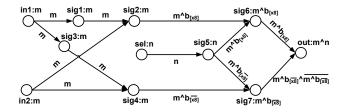

Set of assignments for variables in X that results in feasible behaviors : 1101, 1110

Transformations Resource Estimation Implementability

Propagate feasible behavior assignments onto CPOGs to get feasible CPOGs

- Nodes and edges with value 0 are eliminated

- Node is excluded, if all the incoming edges to a node are excluded

- Node is excluded, if all the outgoing edges of a node are excluded

- All edges originating from an excluded node are also excluded

- All edges terminating on an excluded node are also excluded

- All other nodes and edges are left as such

Algorithm 3 provides the set of feasible CPOGs

Transformations Resource Estimation Implementability

# Algorithm 3: $getFeasibleCPOGs(G, \mathcal{F})$

```

Input: Simplified CPOG G = \langle V, E, X, \rho, \phi \rangle, Feasible behavior assignments for X as \mathcal{F} = \{\langle f_1 \rangle, \dots, \langle f_k \rangle\} //Ex:

\mathcal{F}=\{<1101>,<1110>\}

Output: Set of CPOGs \mathscr{V} = \{G_1, G_2, \dots, G_k\}

Let \mathscr{V} = \{\}:

foreach feasible behavior f_i \in \mathcal{F} do

Let G_i be an instance of G_i

foreach node or edge z \in G_i do

//Evaluate \phi(z) based on f_i value

if \phi(z)|_{f} = 0 then

G_i = G_i - \{z\}; //Remove z from CPOG

//Remove unused edges

if z is node then

Remove all incoming edges to z and Remove all outgoing edges from z:

end

end

end

//Remove isolated nodes

foreach remaining node z \in G; do

Let I_z be the set of incoming edges to z and let O_z be the set of outgoing edges from z;

if I_{z} == \{\} or O_{z} == \{\} then

G_i = G_i - \{z\}; //Remove node z from CPOG

end

end

\mathscr{V} \leftarrow \mathscr{V} \cup G_i; //Add G_i to set \mathscr{V}

end

return 𝒴:

```

Transformations Resource Estimation Implementability

#### Feasible CPOGs with Boolean vector 1101 and 1110

Sandeep K. Shukla, FERMAT Lab, Virginia Tech.

Transformations Resource Estimation Implementability

#### Resources needed

- CPOG has 11 nodes

- Assuming each node requires a computation resource, we need 11 computation resources

Transformations Resource Estimation Implementability

#### Resources needed

- Feasible CPOG with X = 1101 has 8 nodes

- We only require 8 computation resources

Transformations Resource Estimation Implementability

#### Resources needed

- Feasible CPOG with X = 1110 has 8 nodes

- We only require 8 computation resources

The assignments X = 1101, 1110 can be used as opcodes and one can measure latency, power consumption etc in each mode.

Transformations Resource Estimation Implementability

- Propagate feasible behaviors assignment values to the CPOG

- CPOG remains still connected and rooted

- No causal loops

- Then the CPOG is sequentially implementable

- Algorithm 4 checks the implementability

# **Algorithm 4:** *isImplementable*(G)

```

Input: Simplified CPOG G = \langle V, E, X, \rho, \phi \rangle, Feasible behavior assignments for X as \mathcal{F} = \{\langle f_1 \rangle, ..., \langle f_k \rangle\}

Output: True if implementable, else false

Let \mathcal{V} = getFeasibleCPOGs(G, \mathcal{F});

foreach CPOG G_i \in \mathcal{V} do

if G_i has causal loops OR G_i is not weakly connected then

| return false;

end

end

return True;

```

29/30

Outline of the talk

Motivation

- 2 Introduction to CPOGs

- Introduction to MRICDF

- 4 MRICDF Models to CPOGs

- 5 Analysis and ASIP Synthesis

- 6 Conclusion and Future

Conclusion and Future Work Further Reading

**Conclusion and Future Work** Further Reading

### Conclusion and Future Work

Conclusion

- Proposed a new compilation scheme for SIGNAL/MRICDF polychronous specifications based on CPOGs

- Provided algorithms to derive CPOGs from SIGNAL/MRICDF specifications

Future Work

- Explore the aspect of sequential and concurrent implementability by applying transformations on the CPOGs

- Formal proofs

Conclusion and Future Work Further Reading

### Further Reading for CPOGs and ASIPs

Mokhov, A., Sokolov, D., Rykunov, M., Yakovlev, A. Formal modelling and transformations of processor instruction sets – MEMOCODE 2011

#### Mokhov, A., Yakovlev, A.

Conditional Partial Order Graphs: Model, Synthesis and Application – IEEE Transactions on Computers 2010

#### 📚 Kountouris, A.A., Wolinski, C.

Hierarchical conditional dependency graphs as a unifying design representation in the CODESIS high-level synthesis system – ISSS 2000

Mokhov, A., Iliasov, A., Sokolov, D., Rykunov, M., Yakovlev, A., Romanovsky, A. Synthesis of Processor Instruction Sets from High-Level ISA Specifications – IEEE Transactions on Computers 2013

#### Singh, S.

Hardware/Software Synthesis and Verification Using Esterel - CPA 2007

#### Mathworks Inc.

HDL Coder: Generate Verilog and VHDL code for FPGA and ASIC Designs

Conclusion and Future Work Further Reading

### Further Reading for MRICDF and Polychrony

Paul Le Guernic, Jean-Pierre Talpin, Jean-Christophe Le Lann Polychrony for system design – Journal for Circuits, Systems and Computers 2003

Bijoy A. Jose, Sandeep K. Shukla An alternative polychronous model and synthesis methodology for model-driven embedded software – ASP-DAC 2010

M Nanjundappa, M Kracht, J Ouy and SK Shukla A novel technique for correct-by-construction concurrent code synthesis from polychronous specifications – ACSD 2013

Bijoy A. Jose, Jason Pribble, Sandeep K. Shukla Faster Software Synthesis Using Actor Elimination Techniques for Polychronous Formalism – ACSD 2010

J. Brandt, M. Gemunde, K. Schneider, S. Shukla, and J.-P. Talpin.

Embedding polychrony into synchrony – In IEEE Transactions on Software

Engineering, 2012.

# Any Questions??

Thank You!!